一个由许多寄存器组成的数字系统, 必须提供将信息从一个寄存器传输到另一个寄存器的路径。如果在系统中每个寄存器和所有其他寄存器之间使用单独的线, 则连接所有寄存器的导线数量将过多。

另一方面, 总线结构对于在多寄存器配置系统中的寄存器之间传输信息更有效。

总线由一组公用线组成, 每条寄存器的每一位公用一条, 二进制信息一次通过一条公用线传输。控制信号确定在特定寄存器传输期间总线选择哪个寄存器。

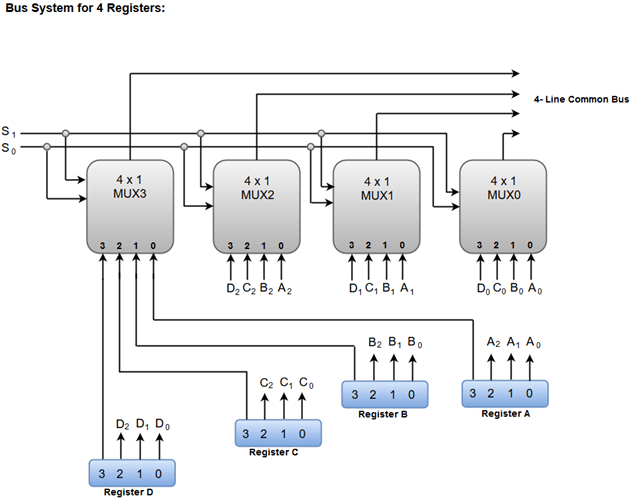

以下框图显示了具有四个寄存器的总线系统。它由四个4 * 1多路复用器构成, 每个多路复用器具有四个数据输入(0至3)和两个选择输入(S1和S2)。

我们使用标签来使你更方便地了解四个寄存器的总线系统的输入输出配置。例如, 寄存器A的输出1连接到MUX1的输入0。

两条选择线S1和S2连接到所有四个多路复用器的选择输入。选择线选择一个寄存器的四位并将它们传输到四线公共总线中。

当两条选择线均处于低逻辑电平时, 即S1S0 = 00, 则选择所有四个多路复用器的0数据输入并将其施加到构成总线的输出上。这又使总线接收寄存器A的内容, 因为该寄存器的输出连接到多路复用器的0数据输入。

同样, 当S1S0 = 01时, 选择寄存器B, 并且总线将接收寄存器B提供的内容。

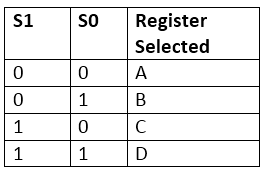

下表列出了总线为选择线的四个可能的二进制值中的每一个选择的寄存器。

注:构造总线所需的多路复用器数量等于每个寄存器中的位数。每个多路复用器的大小必须为“ k * 1”, 因为它会多路复用“ k”条数据线。例如, 用于八个16位寄存器的公共总线每个都需要16个多路复用器, 总线中的每一行一个。每个多路复用器必须具有八条数据输入线和三条选择线, 以多路复用八个寄存器中的一个有效位。

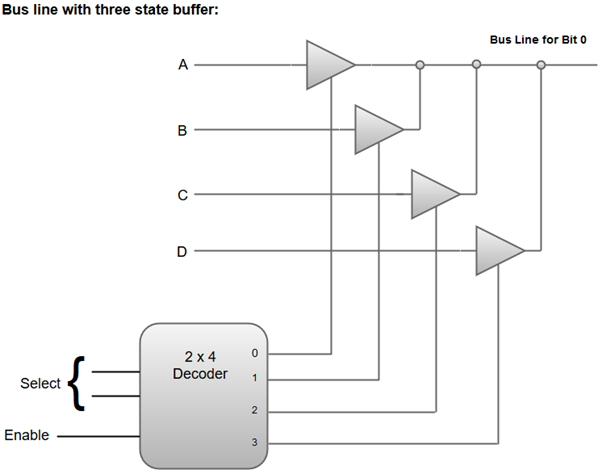

也可以使用三态门代替多路复用器来构建总线系统。

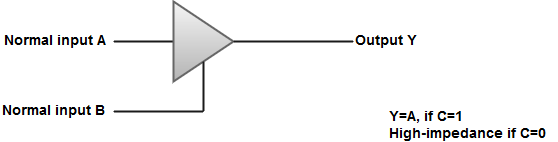

可以将这三个状态门视为具有三个门的数字电路, 其中两个是与常规门相同的逻辑1和0信号。但是, 第三栅极呈现高阻抗状态。

在总线系统中, 最常用的三个状态门是缓冲门。

三态缓冲门的图形符号可以表示为:

下图说明了具有三态缓冲器的总线系统的构造。

- 由四个缓冲器产生的输出被连接以形成一条总线。

- 在给定的时间点, 只有一个缓冲区可以处于活动状态。

- 缓冲器的控制输入确定四个正常输入中的哪个将与总线通信。

- 2 * 4解码器可确保在任何给定时间点激活的控制输入不超过一个。

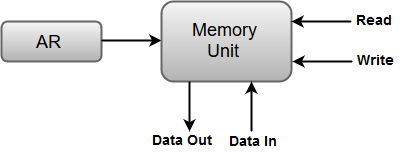

记忆转移

下面说明用于指定内存传输操作的大多数标准符号。

- 从存储单元到用户端的信息传输称为读取操作。

- 要存储在存储器中的新信息的传输称为写操作。

- 记忆字由字母M表示。

- 编写存储器传输操作时, 必须指定存储器字的地址。

- 地址寄存器由AR指定, 数据寄存器由DR指定。

- 因此, 读取操作可以表示为:

Read: DR ← M [AR]- Read语句导致信息从地址寄存器(AR)选择的存储字(M)传输到数据寄存器(DR)中。

- 相应的写操作可以表示为:

Write: M [AR] ← R1- Write语句导致信息从寄存器R1传输到地址寄存器(AR)选择的存储字(M)中。

srcmini

srcmini

评论前必须登录!

注册