本文概述

使用硅材料制造集成电路(IC), 并将其安装在陶瓷或塑料容器(称为芯片)中。 IC的基本组件由用于数字门的电子电路组成。各种栅极在IC内部互连以形成所需的电路。

以下类别可以将集成电路(IC)大致分类:

SSI(小型集成设备)

这些类型的器件在一个封装中包含多个独立的门。这些门的输入和输出直接连接到封装中的引脚。逻辑门的数量通常少于10个, 并受IC中可用引脚数的限制。

MSI(中型规模集成设备)

在单个封装中, 此类器件的复杂度约为10至200个门。基本组件包括解码器, 加法器和寄存器。

LSI(大型集成设备)

LSI器件在一个封装中包含大约200至数千个门。 LSI设备的基本组件包括数字系统, 例如处理器, 存储芯片和可编程模块。

VLSI(大型集成设备)

这种类型的设备在单个封装中包含数千个门。 VLSI设备最常见的示例是复杂的微型计算机芯片。

数字集成电路也通过其所属的特定电路技术进行分类。电路技术通常被称为数字逻辑家族。每种技术都有其自己的基本电子电路和要执行的功能。

每种技术中最常见的组件是NAND, NOR或反相器门。

数字逻辑系列中最受欢迎的包括:

- TTL(晶体管-晶体管逻辑)

- ECL(发射极耦合逻辑)

- MOS(金属氧化物半导体)

- CMOS(互补金属氧化物半导体)

TTL(晶体管-晶体管逻辑)

TTL技术是先前称为DTL(二极管晶体管逻辑)的技术的升级版本。 DTL技术过去具有基本NAND门的二极管和晶体管。当将这些二极管替换为晶体管以改善电路操作时, 就存在TTL。

TTL有多种变体, 例如高速TTL, 低功耗TTL, 肖特基TTL, 低功耗肖特基TTL和高级肖特基TTL。

下图显示了标准TTL电路及其配置。

TTL系列的功能:

- TTL电路的总电源电压为5伏, 两个逻辑电平分别约为0和3.5伏。

- TTL电路的输出最多可以支持10个门。

- TTL电路的平均传播延迟约为9ns。

TTL应用

- TTL用作驱动灯和继电器的开关设备。

- TTL在控制器应用中用于提供0至5V。

- TTL系列主要用于DEC VAX等小型计算机的处理器中。

- 它也用于打印机和视频显示终端。

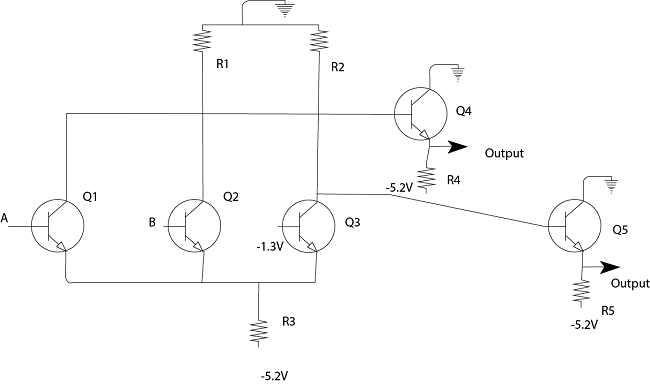

ECL(发射极耦合逻辑)

ECL技术以集成形式提供了最快的数字电路。 ECL电路用于需要高速的超级计算机和信号处理器中。

ECL栅极中的晶体管在非饱和状态下运行, 该条件允许实现1-2纳秒的传播延迟。

ECL系列的功能

- 即使在非活动状态下, 逻辑门也持续汲取电流。因此, 与其他逻辑系列相比, 功耗更大。

- ECL使用双极晶体管逻辑, 其中晶体管不在饱和区域工作。

- ECL门的平均传播延迟约为0.5至2ns。

MOS(金属氧化物半导体)是一种单极晶体管, 仅取决于一种载流子的流量, 该载流子可以是电子(n沟道)或空穴(p沟道)。

MOS技术通常分为两种基本形式:

- P沟道MOS被称为PMOS。

- n沟道MOS称为NMOS。

功率MOS

可以通过考虑PMOS NAND门来解释PMOS逻辑系列执行的操作。

下图显示了两个输入的PMOS NAND门。

将低逻辑应用于A或B时, 晶体管将被激活。这样可以在电源和输出端子之间建立连接。

当施加低逻辑时, 输出升高到逻辑高值。否则, 在其他情况下它将保持逻辑低电平。

除非向A或B施加低电平逻辑, 否则下拉电阻器’R’保持低电平逻辑。

NMOS

NMOS逻辑的结构类似于PMOS。但是, 在这里, 我们将使用NMOS晶体管以及上拉电阻R来代替PMOS晶体管。

以下电路图显示了两个输入NMOS NAND门。

如电路图所示, NMOS NAND门具有两个从输出端到接地端串联的NMOS晶体管。

上拉电阻器从输出端子连接到电源。

当高逻辑被施加到两个输入时, 两个晶体管都被激活。这将在输出端子和接地之间建立连接。

如果输入中的任何一个处于逻辑高电平, 而另一个则处于逻辑低电平, 则晶体管将被停用。这终止了输出端子和地面之间的路径。

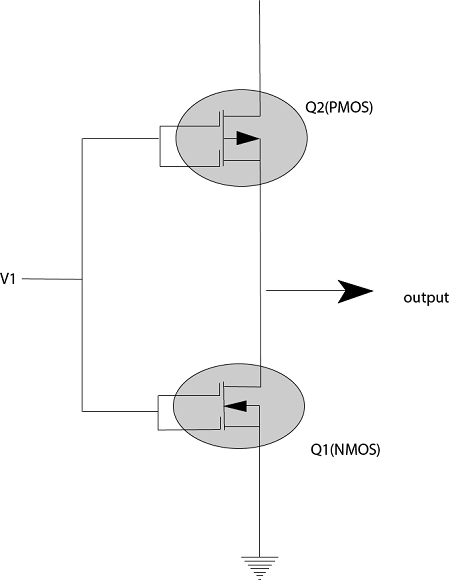

CMOS(互补金属氧化物半导体)

互补MOS或CMOS技术使用在所有电路中以互补方式连接的PMOS和NMOS晶体管。

CMOS逻辑系列因其高抗噪性和低功耗而在大型集成电路中受到高度青睐。

以下电路图显示了标准CMOS电路及其配置。

Q1和Q2是互补连接的NMOS和PMOS晶体管。

srcmini

srcmini

评论前必须登录!

注册